# **Real Time Clock Circuit**

### **Features**

- Battery pin, bus disabled on power down

- Easy to use like a RAM with fast access time

- Interface compatible with both Intel and Motorola microprocessors

- TTL/CMOS compatible

- Standby on power down typically 5  $\mu$ A

- Chrono and alarm time interrupt

- Can be synchronized to a master clock pulse

- Pulse output once per second, minute or hour

- BUSY pin can be used as a 1 Hz strobe for display control

- BCD data format

- Leap-year and auto roll-over of week number

- Packages DIP 16 and SO 16

- SYNC pin to tune the device to an external time reference

- Frequency tuning and test modes

## Description

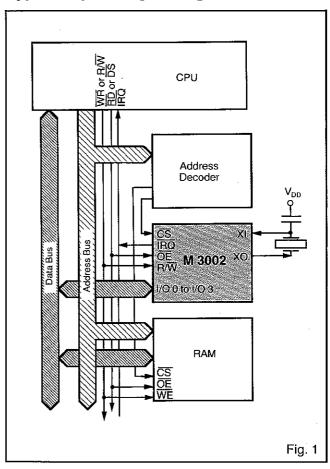

The M 3002 is a monolithic low power CMOS device which functions as a 4 bit real time clock. The device is accessed by chip select  $(\overline{CS})$  with read and write function timing provided by  $\overline{OE}$  and  $R/\overline{W}$ . The M 3002 is driven by an external 32.768 kHz crystal, and uses the 24 hour system. An alarm can be preprogrammed up to one month in advance. The timer can measure elapsed time up to 24 hours. Time data is stored in a 15 by 8 bit RAM in BCD format. An 8 bit status word in the RAM controls the mode of operation.

# **Applications**

- Single board computers

- Industrial controllers

- PABX and telephone systems

- Taximeters, lorry tachos

- Data loggers

## Typical Operating Configuration

# **Pin Assignment**

## **Absolute Maximum Ratings**

| Parameter                                                                                                                                                                                     | Symbol                                                                                                                                            | Conditions                                                                                                                                                                                             |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Maximum voltage at V <sub>DD</sub> Minimum voltage at V <sub>DD</sub> Maximum voltage at XI and XO Minimum voltage at XI and XO Max. voltage at any signal pin Min. voltage at any signal pin | V <sub>DD max</sub><br>V <sub>DD min</sub><br>V <sub>max</sub><br>V <sub>min</sub><br>V <sub>max</sub><br>V <sub>min</sub><br>T <sub>STOmax</sub> | $V_{SS} + 8.0 \text{ V}$ $V_{SS} - 0.3 \text{ V}$ $V_{DD} + 0.3 \text{ V}$ $V_{BB} - 0.3 \text{ V}$ $V_{DD} + 0.3 \text{ V}$ $V_{SS} - 0.3 \text{ V}$ $+ 150 ^{\circ}\text{C}$ $- 65 ^{\circ}\text{C}$ |

Table 1

Stresses above these listed maximum ratings may cause permanent damage to the device. Exposure beyond specified operating conditions may affect device reliability or cause malfunction.

## **Handling Procedures**

This device has built-in protection against high static voltages or electric fields; however, anti-static precautions must be taken as for any other CMOS component. Unless otherwise specified, proper operation can only occur when all terminal voltages are kept within the supply voltage range. Unused inputs must always be tied to a defined logic voltage level.

## **Operating Conditions**

| Parameter                     | Symbol            | Min. | Тур.   | Max. | Units |

|-------------------------------|-------------------|------|--------|------|-------|

| Operating temperature         | TA                | -40  |        | +85  | °C    |

| Logic supply voltage          | $V_{DD}$          | +2.4 | +5.0   | +5.5 | V     |

| Battery voltage <sup>1)</sup> | $V_{DD} - V_{BB}$ | +2.4 |        | +5.0 | V     |

| Crystal Characteristics       |                   |      | ]      |      |       |

| Frequency <sup>2)</sup>       | f                 |      | 32.768 |      | kHz   |

| Load capacitance              | C <sub>L</sub>    | 8    | 10     | 13   | pF    |

| Series resistance             | $R_s$             |      | 20     | 50   | kΩ    |

| Trimmer capacitance           | C <sub>T</sub>    | 5    | 15     | 40   | рF    |

<sup>1)</sup> See Fig. 10 and Fig. 11

Table 2

## **Electrical Characteristics**

$V_{DD}=5.0~V\pm10\%$  ,  $V_{SS}=0~V,~V_{BB}=3.0~V,$  and  $T_{A}=0^{\circ}C$  to  $+70^{\circ}C,$  unless otherwise specified

| Parameter                     | Symbol           | Test Conditions                                         | Min. | Тур. | Max. | Units   |

|-------------------------------|------------------|---------------------------------------------------------|------|------|------|---------|

| Total static supply           | I <sub>DD</sub>  | all outputs open,<br>all inputs at V <sub>DD</sub>      |      |      | 10   | μΑ      |

| Standby current               | l <sub>BB</sub>  | $V_{DD} = 0 V$                                          |      | 5    | 8    | $\mu$ A |

| Inputs and Outputs            |                  |                                                         |      |      |      |         |

| Input logic low               | V <sub>IL</sub>  |                                                         | 0.0  |      | 0.8  | V       |

| Input logic high              | V <sub>iH</sub>  |                                                         | 2.4  |      | 5.0  | V       |

| Pullup on OE and SYNC pins    | 1 <sub>E</sub>   | $V_{IL} = 0.8 V$                                        | 30   |      |      | $\mu$ A |

| Output logic low on I/O pins  | V <sub>OL</sub>  | $I_{OL} = 3.2 \text{mA}$                                |      |      | 0.4  | V       |

| Output logic low              | V <sub>OL</sub>  |                                                         |      |      | 0.4  | V       |

| Output logic high on I/O pins | V <sub>OH</sub>  | $I_{OH} = 2 \text{ mA}$                                 | 2.4  |      |      | V       |

| Output logic high on IRQ      | V <sub>OH</sub>  | 100k pullup to V <sub>DD</sub>                          | 2.4  |      | -    | V       |

| Output logic high             | V <sub>OH</sub>  |                                                         | 2.4  |      |      | V       |

| Input leakage                 | I <sub>IN</sub>  | $0.0 < V_{IN} < 5.0$                                    |      |      | 1    | $\mu$ A |

| Oscillator                    |                  |                                                         |      |      |      |         |

| Starting voltage              | V <sub>STA</sub> | $C_T = 18pF$                                            | 1.8  |      |      | V       |

| Input capacitance on XI       | CiN              |                                                         |      | 3.7  |      | pF      |

| Output capacitance on XO      | Cout             |                                                         |      | 25   |      | pF      |

| Start-up time                 | T <sub>STA</sub> | $C_T = 18pF$                                            |      | 0.6  | 5    | s       |

| Frequency stability           | ∆f/f             | $2.0 \le V_{BB} \le 5.0 \text{ V}$ $C_T = 5 \text{ pF}$ |      | 5    | 10   | ppm/V   |

Table 3

<sup>2)</sup> Parallel resonant crystal

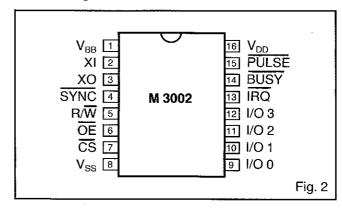

## **Timing Characteristics**

$V_{DD} = 5.0~\text{V} \pm 10\%,\, V_{SS} = 0~\text{V},\, V_{BB} = 3.0~\text{V},\, \text{and}\,\, T_{A} = 0^{\circ}\text{C}\,\, \text{to}\, + 70^{\circ}\text{C}$

| Parameter                                | Symbol           | Test Conditions | Min. | Тур. | Max. | Units |

|------------------------------------------|------------------|-----------------|------|------|------|-------|

| Chip select duration                     | t <sub>CS</sub>  |                 | 280  |      |      | ns    |

| RAM access time1)                        | t <sub>ACC</sub> |                 |      | 150  | 270  | ns    |

| Time between two transfers               | tw               |                 | 1000 |      |      | l ns  |

| Data valid to Hi-impedance <sup>2)</sup> | t <sub>DF</sub>  |                 |      | 180  | 300  | ns    |

| Write data settle time <sup>3)</sup>     | t <sub>DW</sub>  |                 | 200  |      | 1    | ns    |

| Data hold time <sup>4)</sup>             | t <sub>DH</sub>  |                 | 0    |      |      | ns    |

Table 4

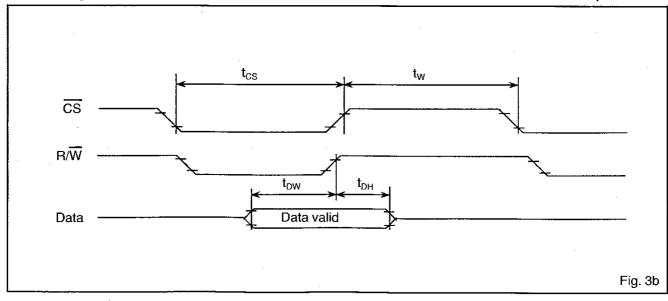

# **Timing Waveforms**

Read Timing for Both Intel (RD and WR Pulse) and Motorola (Advanced R/W with OE Tied to CS)

## Write Timing for Both Intel (RD and WR Pulse) and Motorola (Advanced R/W with OE Tied to CS)

<sup>1)</sup> t<sub>ACC</sub> starts from  $\overline{OE}$  or  $\overline{CS}$ , whichever activates last.

2) t<sub>DF</sub> starts from  $\overline{OE}$  or  $\overline{CS}$ , whichever deactivates first.

3) t<sub>DW</sub> ends at R/W or  $\overline{CS}$ , whichever deactivates first.

4) t<sub>DH</sub> starts from R/W or  $\overline{CS}$ , whichever deactivates first.

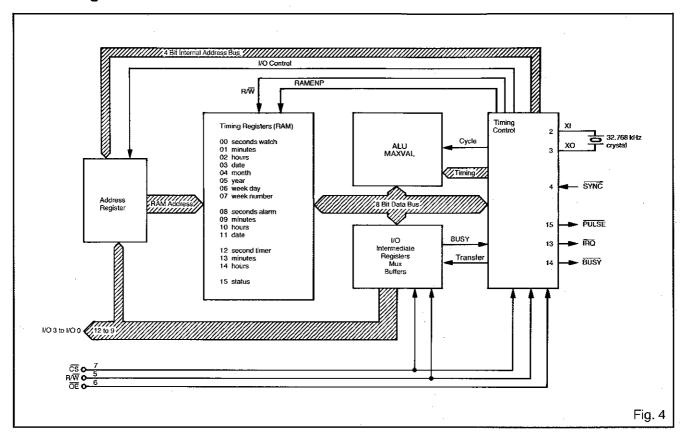

## **Block Diagram**

## **Pin Description**

| Pi | n   | Name            | Function                                                 |  |  |  |

|----|-----|-----------------|----------------------------------------------------------|--|--|--|

| 1  | 1   | V <sub>BB</sub> | Negative battery terminal                                |  |  |  |

| 2  | 2   | XĬ.             | 32.768 kHz quartz input                                  |  |  |  |

| 3  | 3   | XO              | 32.768 kHz quartz output                                 |  |  |  |

| 2  | 1   | SYNC            | Time synchronization input                               |  |  |  |

|    |     |                 | (internal pullup)                                        |  |  |  |

| 5  | 5   | R/W             | $\overline{WR}$ (Intel) or R/ $\overline{W}$ (Motorola), |  |  |  |

| ł  |     |                 | see Fig. 10 and 11                                       |  |  |  |

| 6  | 3   | ŌĒ              | RD (Intel), see Fig. 10 and 11                           |  |  |  |

|    |     |                 | (internal pullup)                                        |  |  |  |

| 7  | 7   | <del>CS</del>   | Chip select input                                        |  |  |  |

| 8  | 3   | $V_{SS}$        | Ground terminal                                          |  |  |  |

|    |     | I/O 0           | )                                                        |  |  |  |

| 10 | ) [ | I/O 1           | Data bus input/output lines                              |  |  |  |

| 11 | 1   | 1/02            | Address bus input lines                                  |  |  |  |

| 12 | 2   | <u>I/O3</u>     | ,                                                        |  |  |  |

| 13 | 3   | IRQ             | Interrupt request output (open drain                     |  |  |  |

|    | ٠   |                 | with internal pullup)                                    |  |  |  |

| 14 | 4   | BUSY            | Internal update cycle status output                      |  |  |  |

| 15 | 5   | PULSE           | Programmable timing pulse output                         |  |  |  |

| 16 | 6   | $V_{DD}$        | Positive supply terminal (substrate)                     |  |  |  |

Table 5

## **Functional Description**

### **Power Supply and Data Retention**

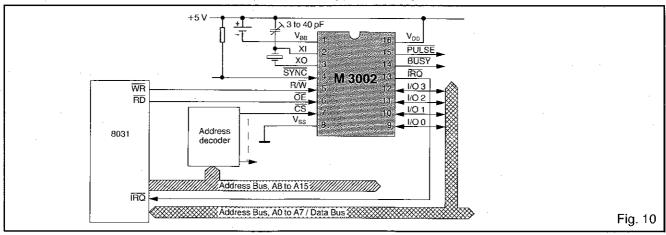

The M 3002 can be powered with a supply voltage between 2.4 and 5.5 V, and backed up with a battery or supercap (2.4 to 5.0 V), as indicated in Fig. 10 and 11, to ensure operation and data retention during power-down. Because of the low power consumption of the device, lithium cells or standard rechargeable cells give many years of effective life. If the battery is not required then connect  $V_{BB}$  to  $V_{SS}$ . When the voltage at the  $V_{BB}$  pin drops below the voltage at the  $V_{SS}$  pin, access to the device is disabled. The I/O lines and the outputs  $\overline{BUSY}$  and  $\overline{PULSE}$  are set to a high impedance state. The opendrain output  $\overline{IRQ}$  will be inactive until  $V_{DD}$  is restored. Care should be taken to avoid the occurance of improper states on interfacing signal lines.

#### RAM

The 16 x 8 RAM is used to store all clock, alarm, timer and status data. The allocation of RAM addresses is shown in Table 6. All time data are stored in Binary Coded Decimal (BCD) format. The transfer of this data between the internal 8-bit bus and the I/O lines is performed by the bidirectional I/O buffer (see Block Diagram Fig. 4). If the alarm and timer functions are not needed, then the RAM section from these functions, addresses 8 to  $\dot{E}$  hex, may be used as non-volatile system storage by software. It should be noted however that, if the unused function is inadvertently activated by altering the status word, the

stored data may be modified.

#### I/O Address Locations

|   | ress<br>Dec | Data     | Group  | Max. Value     | Operations       |

|---|-------------|----------|--------|----------------|------------------|

| 0 | 0           | Seconds  | Watch  | 59             | Time data        |

| 1 | 1           | Minutes  |        | 59             | incremented      |

| 2 | 2           | Hours    |        | 23             | under control of |

| 3 | 3           | Date     |        | 28, 29, 30, 31 | status bit 0     |

| 4 | 4           | Month    |        | 12             |                  |

| 5 | 5           | Year     |        | 99             |                  |

| 6 | 6           | Week day |        | 07             |                  |

| 7 | 7           | Week no. |        | 53             |                  |

| 8 | 8           | Seconds  | Alarm  | 59             | Alarm data,      |

| 9 | 9           | Minutes  |        | 59             | providing an IRQ |

| Α | 10          | Hours    |        | 23             | under control of |

| В | 11          | Date     |        | 28, 29, 30, 31 | status bit 1     |

| С | 12          | Seconds  | Timer  | 59             | Timer data       |

| D | 13          | Minutes  |        | 59             | incremented      |

| Ε | 14          | Hours    |        | 23             | under control    |

|   |             |          |        |                | of status bit 4  |

| F | 15          | Status   | Status |                | Control          |

Table 6

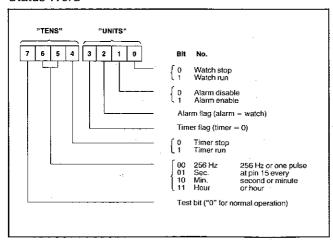

#### Status and Control

The function of the individual bits of the status word are shown in Table 7. The status word, address F hex, controls the timekeeping functions performed in the ALU section of the M 3002 (see Block Diagram Fig. 4). The status word must be written on recovery from a total power loss,  $V_{DD}$  and the battery voltage < 2.4 V.

## Status Word

Table 7

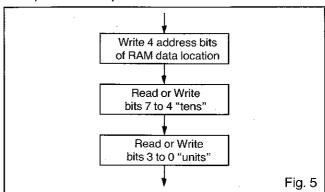

#### **RAM Access**

The interface between the M 3002 and the host microprocessor consists of four bidirectional multiplexed data/address lines (I/O lines), three control lines ( $\overline{CS}$ ,  $\overline{OE}$ , R/W), and an interrupt request line ( $\overline{IRQ}$ ). Three steps are required to access a RAM address. The first access transfers the 4-bit address of the data location, the second reads or writes data bits 7 to 4 (tens) to or from the address written in step one, and the third reads or

writes data bits 3 to 0 (units). Fig. 5 shows the 3 step access sequence.

#### 3 Step Access Sequence

An internal multiplexer defines the 3 step access sequence position. A 3 step access sequence is began by writing the RAM 4-bit address and then the M 3002 treats the next two accesses as the 4-bit data transfers, tens first, units second. A read access, while the multiplexer is expecting an address write, will not begin a 3 step access sequence. The multiplexer can be initialized (expecting an address write) by two read accesses. Read accesses will complete a 3 step access sequence, but will not begin one. The multiplexer must be initialized by software on every power up of the system including power up of the M 3002 from a power loss ( $V_{DD}$  and the battery voltage < 2.4 V) condition.

#### **RAM Access and Internal Update Cycles**

Every second an internal update occurs and lasts between 0.73 ms and 6 ms. During this update cycle, the multiplexer is initialized, the BUSY output is active, and a read will give F hex on the I/O pins. The RAM is allocated to the ALU (see Block Diagram Fig. 4). If an external data transfer is in progress (see RAM Access section), the internal update cycle is delayed for a maximum of one second. After a delay of one second the external data transfer will be aborted and the RAM assigned to the internal update cycle. With the multiplexer in its initial state, reading the M 3002 will give 0 hex if an internal update cycle is not in progress and F hex if in progress. Thus prior to beginning a 3 step access sequence, software must read the I/O pins to determine if the RAM is available. Additionally the BUSY pin goes active while an internal update cycle is in progress. To prevent an update during a sequence of transfers, for example hours, minutes and seconds, there must be less than 2 ms between each transfer (i.e. 3 step access sequence). If software continuously polls the M 3002 to seek an event or refresh a display then the delay between two poll sequences (e.g. read hours, minutes, seconds) should be greater than 6 ms to allow an update cycle to occur.

### **RAM Access and Interrupts**

Any false or aborted access will make the M 3002 jump incorrectly to the next step in the 3 step access sequence. Access to the M 3002 is not re-entrant and so

the software routine accessing the M 3002 must complete the 3 step access sequence before another software routine can access the device. Interrupt software routines must not access the M 3002 unless it can be guaranteed that the M 3002 is not in a 3 step access sequence. Additionally interrupt software routines must not delay the 3 step access sequence in the background routine longer than one second or an internal update cycle will occur within the M 3002. It is recommended that all software routines reading or writing to the M 3002 call one of the software routine structures, shown in Fig. 6, for each device access.

#### M 3002 Software Access Routines

M 3002 WRITE:

Disable maskable interrupts

Wait for Bus = 0 hex

Write address to M 3002

Write data bits 7 to 4 to M 3002

Write data bits 3 to 0 to M 3002

Enable maskable interrupts

M 3002 \_\_ READ:

Disable maskable interrupts

Wait for Bus = 0 hex

Write address to M 3002

Read data bits 7 to 4 from M 3002

Read data bits 3 to 0 from M 3002

Enable maskable interrupts

Fig. 6

Non maskable interrupt routines must not access the M 3002 as it cannot be guaranteed that the M 3002 is not in the middle of a 3 step access sequence. In a multitasking software environment the task accessing the M 3002 must not be interrupted during a 3 step access sequence.

#### Alarm and IRQ

An alarm date and time may be preset in RAM addresses 8 to B hex. During every update cycle, the ALU (see Block Diagram Fig. 4) compares the contents of the watch addresses, 0 to 3 hex, with the preset alarm time data. If the alarm is enabled (status word bit 1) and the alarm time data matches the watch addresses 0 to 3 hex, the IRQ pin goes active and the alarm flag (status word bit 2) is set to indicate to the software the source of the interrupt. IRQ will remain active until the software acknowledges the interrupt by clearing the alarm flag (status word bit 2). If the alarm is enabled (status word bit 1), and an alarm RAM location set to FF hex, this location is not compared with the associated watch location. Thus it is possible to achieve a repeat feature where an alarm occurs every programmed number of, seconds, or seconds and minutes, or seconds, minutes and hours. The M 3002 does not generate interrupts until the 3 step access sequence is complete.

## Timer and IRQ

By setting the status word bit 4 (timer enable bit), the preset time data in RAM addresses C hex to E hex, increments every second with the update cycle. When passing from 23:59:59 to 00:00:00, the timer flag (status word bit 3) is set and the  $\overline{IRQ}$  output goes active.  $\overline{IRQ}$  will remain active until software acknowledges the interrupt by clearing the timer flag (status word bit 3). The M 3002 does not generate interrupts until the 3 step access sequence is complete.

### **PULSE** Output

The  $\overline{\text{PULSE}}$  output can be programmed with bits 5 and 6 of the status word, as shown in Table 7, to produce a negative pulse of 64  $\mu\text{s}$  duration, every second, minute, or hour, while the watch is running. Clearing bits 5 and 6 of the status word will produce a 256 Hz square wave on the  $\overline{\text{PULSE}}$  pin. The latter feature is intended for frequency tuning, see section Frequency Tuning.

## SYNC Input

If the  $\overline{\text{SYNC}}$  input is set low for longer than 200  $\mu\text{s}$ , the watch will synchronize to the falling edge of this  $\overline{\text{SYNC}}$  signal with a precision of  $\pm$  2 ms. The seconds RAM location (address 0 hex) will be cleared and if the contents were  $\geq$  30, the minutes location (address 1 hex) will be incremented.

## **Frequency Tuning**

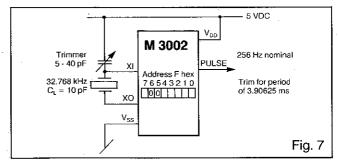

The PULSE pin will output a 256 Hz square wave signal if the bits 5 and 6 of the status word are cleared. The period of the signal on the PULSE pin can be adjusted by the crystal trimmer. The nominal period for 256 Hz is 3.90625 ms (see Fig. 7)

#### Calibration Circuit

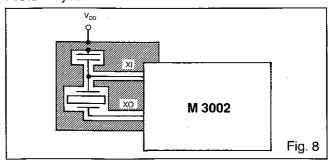

### **Crystal Layout**

In order to ensure proper oscillator operation we recommend the following standard practices.

- Keep traces as short as possible

- Use a guard ring around the crystal and capacitor or trimmer.

Fig. 8 shows the recommended layout.

#### P.C.B. Layout

#### Test

Some of the various test features added to the M 3002, some can be activated by software. Table 8 shows the available test modes and how they may be activated.

**Test Modes**

| Status<br>bit 7 | Status<br>bit 5 | SYNC<br>input   | Function                                                                                                                                                                                      |

|-----------------|-----------------|-----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0               | 0               | $V_{SS}$        | Normal operation                                                                                                                                                                              |

| 1               | 0               | V <sub>SS</sub> | First 5 stages of divider chain bypassed: acceleration by a factor of 321)                                                                                                                    |

| 1               | 1               | V <sub>ss</sub> | Parallel increment of all time and timer data at 1 Hz depending on the status of bit 0 and bit 4 <sup>2)</sup>                                                                                |

| 1               | 1               | V <sub>DD</sub> | Parallel increment of all time and timer data at 32 Hz depending on the status of bit 0 and bit 4 First 5 stages of divider chain bypassed: thus acceleration by a factor of 32 <sup>1)</sup> |

<sup>1)</sup> External signal generator to be used

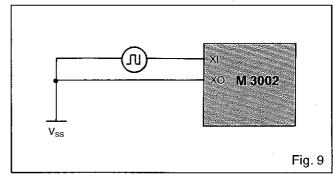

An external signal generator can be used to drive the M 3002. Fig. 9 shows how to connect the signal generator. The speed can be increased by increasing the signal generator frequency to a maximum of 128 kHz. Test modes can be activated while using an external signal generator if required. To leave test, the test bit (status word bit 7) must be cleared by software. Test corrupts the watch and timer data and so all parameters should be reloaded after a test session.

## Signal Generator Connection

# **Typical Application**

## Intel Microprocessor Interfaced with the M 3002 in a Typical Configuration

Table 8

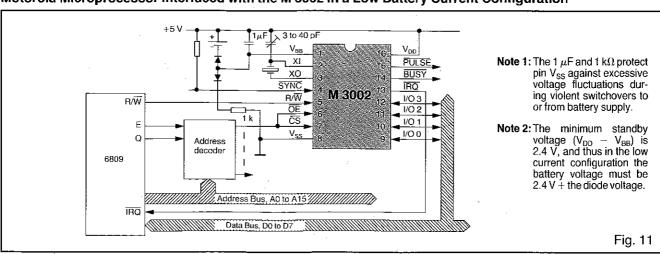

### Motorola Microprocessor Interfaced with the M 3002 in a Low Battery Current Configuration

<sup>2)</sup> Crystal or extended signal generator

## **Package and Ordering Information**

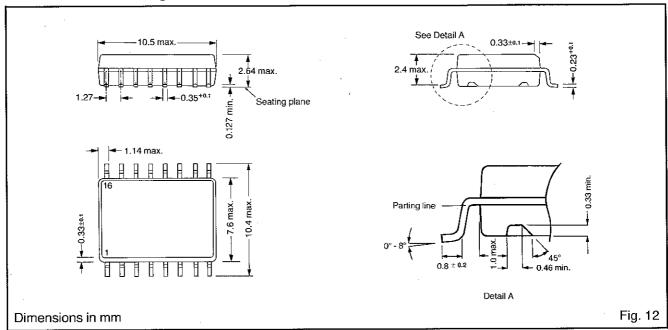

### **Dimensions of SO Package**

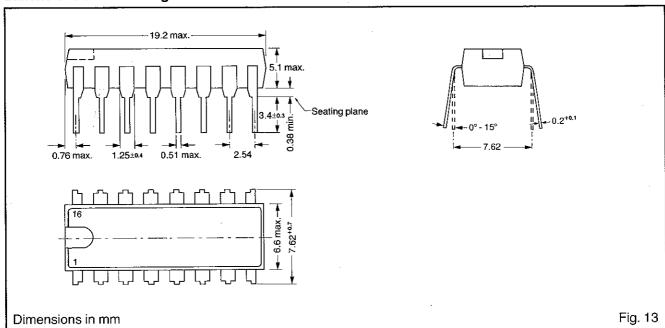

### **Dimensions of DIP Package**

## **Ordering Information**

Chip form on request.

The M 3002 is available in the following packages:

DIP 16-pin plastic package

M 3002 16P

SO 16-pin wide plastic package

M 3002 16S

When ordering, please specify the complete part number and package.

EM Microelectronic-Marin SA cannot assume responsibility for use of any circuitry described other than circuitry entirely embodied in an EM Microelectronic-Marin SA product. EM Microelectronic-Marin SA reserves the right to change the circuitry and specifications without notice at any time. You are strongly urged to ensure that the information given has not been superseded by a more up-to-date version.

E.& O.E. Printed in Switzerland, Th

© 1994 EM-Microelectronic-Marin SA, 08/94, Rev. F/063